Search Results for 'Fpga Sca'

Fpga Sca published presentations and documents on DocSlides.

EEL 5934 Hardware Security Lab

University of Florida HAHA USER MANUAL Contents Ch...

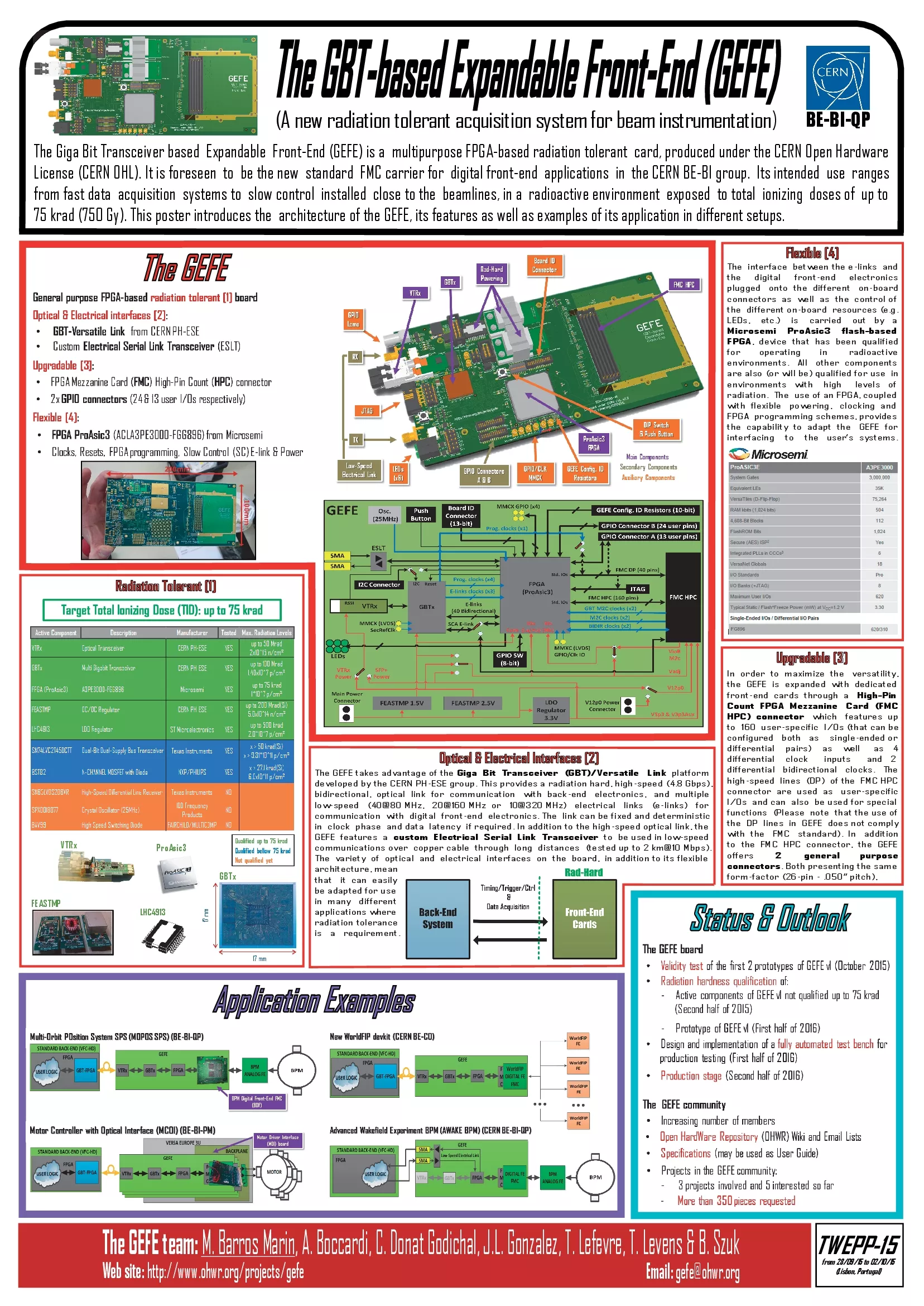

RESEARCH POSTER PRESENTATION

DESIGN

Beam Instrumentation

Technical Board (03 /12/2015) The GBT - based Expa...

1300 Henley Court

Pullman, WA 99163 509.334.6306 www.digilentinc.com...

Application Examples

The GEFE M Barros Marin A Boccardi C Donat Godicha...

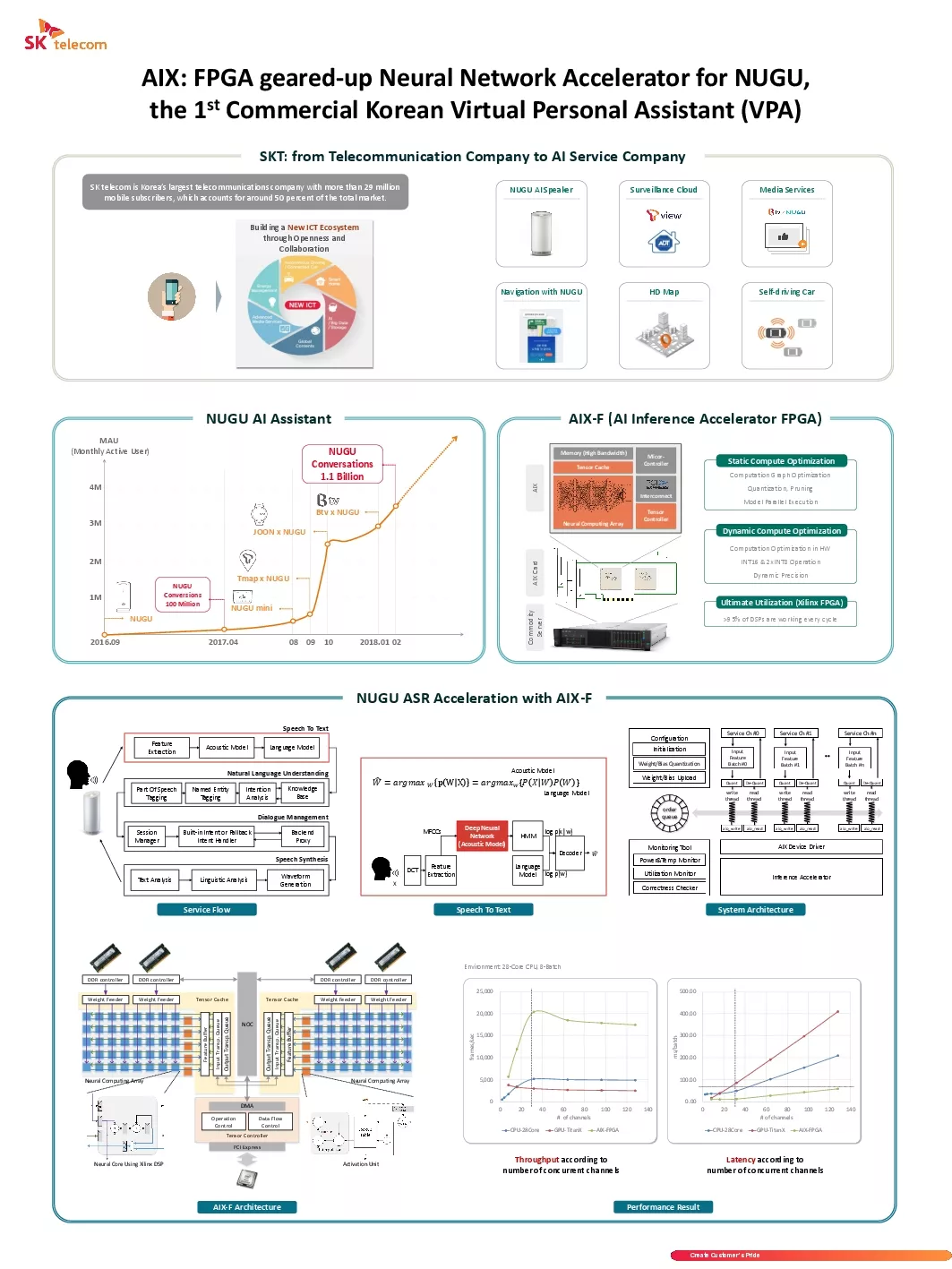

Create Customers Pride

AIX FPGA geared-up Neural Network Accelerator for ...

Generic FPGA based platform for distributed IO in a Proton Therapy Patient Safety Interlock System

. Michael . Eichin. :: HW/FW Engineer :: PSI ...

BER- tester for GEB board

Main . components&restrictions. TLK2501 . seri...

FoCal -E project AGH Team

possible. . contribution. Occupation. . at. AGH...

EECE6017 Lab 7 HPS to FPGA –

Gsensor. to LED. Prelab Activities:. Complete the...

RE-configure FPGA through JTAG

Heidelberg option, needs reprogramming of . Altera...

Test Boards Design for LTDB

Xueye. Hu, . Hucheng. Chen, Joe Mead. USTC &...

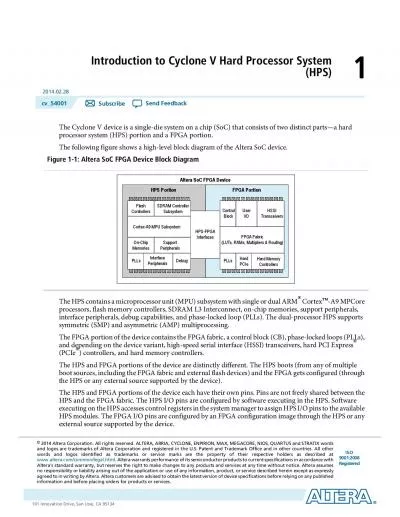

1IntroductiontoCycloneVHardProcessorSystemHPS20140228

cv_54001 Subscribe SendFeedbackTheCycloneVdeviceis...

[DOWLOAD]-EP32 RISC Processor IP: Description and Implementation into FPGA

The Desired Brand Effect Stand Out in a Saturated ...

[PDF]-Computer Architecture Tutorial Using an FPGA: ARM Verilog Introductions

The Desired Brand Effect Stand Out in a Saturated ...

Two FPGA Case Studies Comparing High Level Synthesis and

Manual HDL for HEP applications. Marc-André . Té...

FPGA Based Pico-second Time Measurement System for a DIRC-like TOF Detector

Qiang. Cao. Department of modern physics. Univers...

CDA 4253 FPGA System Design

VHDL . Testbench. Development. Hao Zheng. Comp. ....

FPGA Design Flow ECE

545. Lecture . 10. FPGA . Design process (1). Desi...

FPGA Mezzanine Card standard IO-modules for the LLRF beam control system of CERN’s PS Booster and

MedAustron. synchrotron. M. E. Angoletta, A. Blas...

An introduction to FPGAs and

spatially-pipelined . computing. Andrew W. . Rose....

External scrubber implementation for the ALICE ITS Readout Unit

Magnus Rentsch Ersdal. magnus.ersdal@uib.no. TWEPP...

ECE 44 8 – FPGA and ASIC Design with VHDL

Overview of Embedded . SoC. Systems. ECE . 448. L...

Director: Dr. Vishwani D.

Agrawal. GTA: . Jia. Yao (jzy0001@auburn.edu). ...

Issue with DCLK divider=1 for CLKout0 and 1 (FPGA clock and SYSREF)

DAC38RF82EVM is configured in CMODE3. . Jumper JP1...

1 Digital Circuit Implementation Issues

PLAs, PALs, ROM’s, FPGA’s. ·. . Pa...

ARIETIS An example of NG-Medium usage

Jokin PERRET– 16/03/2023. 1. . EREMS & INNA...

1 High-Performance UVM Verification IP

for . SpaceWire. Codec. Simone Vagaggini. 1,2. , ...

IBERT Testing Update Japnidh Thakral

Lawrence Berkeley National Laboratory. SULI Intern...

BCM FPGA Firmware v4

Code. /. Design. . R. eview. CERN, . 2011-. 0. 5-...

Multithreaded FPGA Acceleration of DNA Sequence Mapping

Edward Fernandez, Walid Najjar, Stefano . Lonardi....

An overview of FPGA use in the LHC accelerator and the CERN experiments.

Dr. Salvatore . Danzeca . EN-STI-ECE. SEFUW. : . S...

![[DOWLOAD]-EP32 RISC Processor IP: Description and Implementation into FPGA](https://thumbs.docslides.com/971293/dowload-ep32-risc-processor-ip-description-and-implementation-into-fpga.jpg)

![[PDF]-Computer Architecture Tutorial Using an FPGA: ARM Verilog Introductions](https://thumbs.docslides.com/987149/pdf-computer-architecture-tutorial-using-an-fpga-arm-verilog-introductions.jpg)